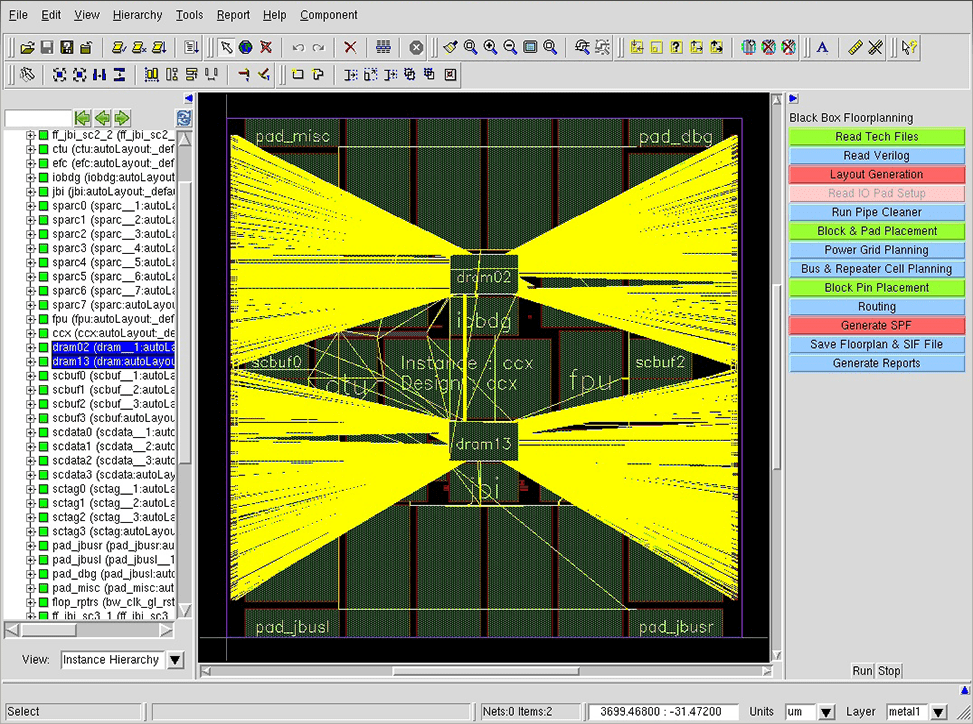

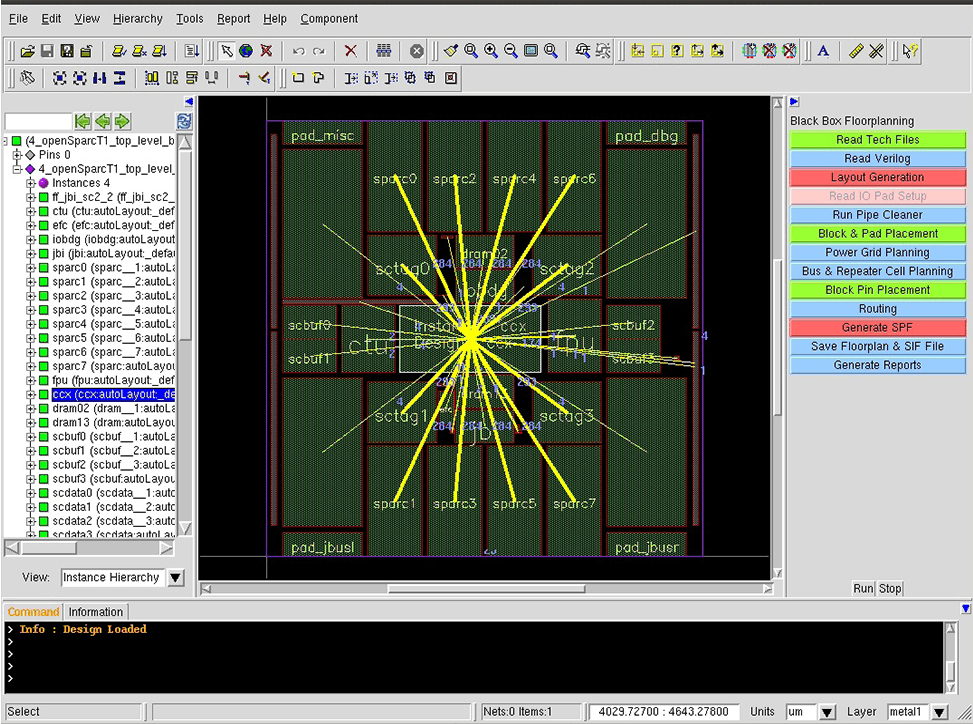

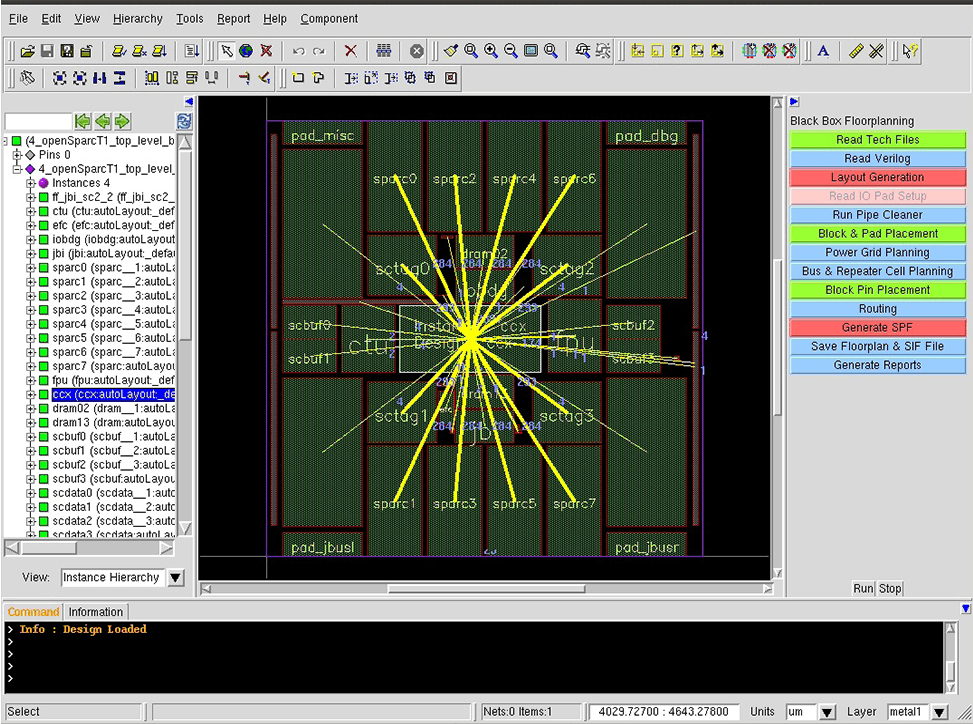

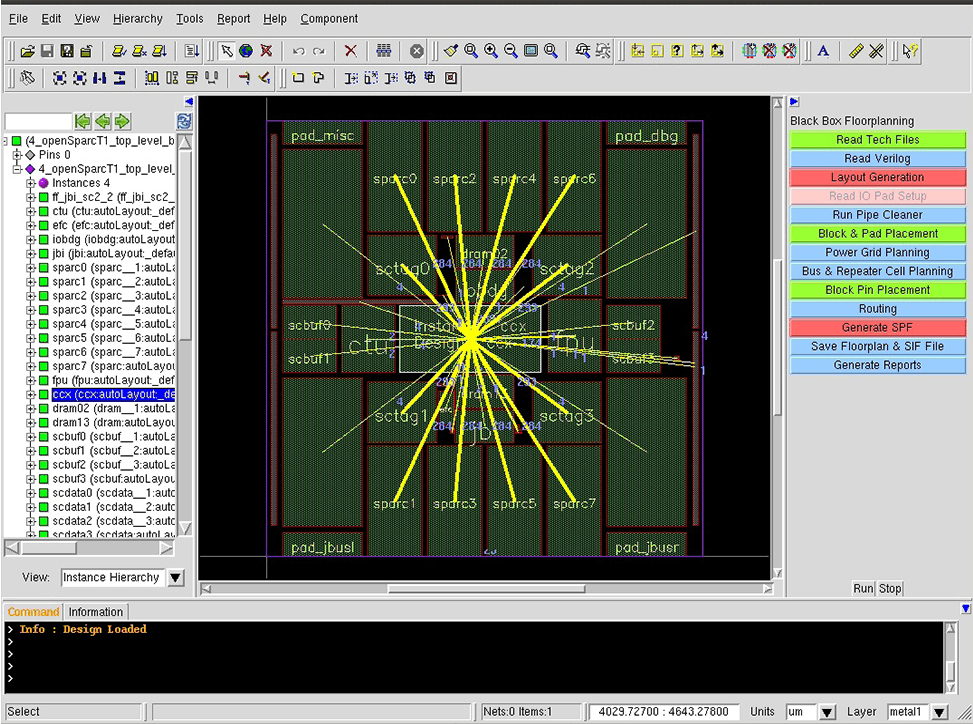

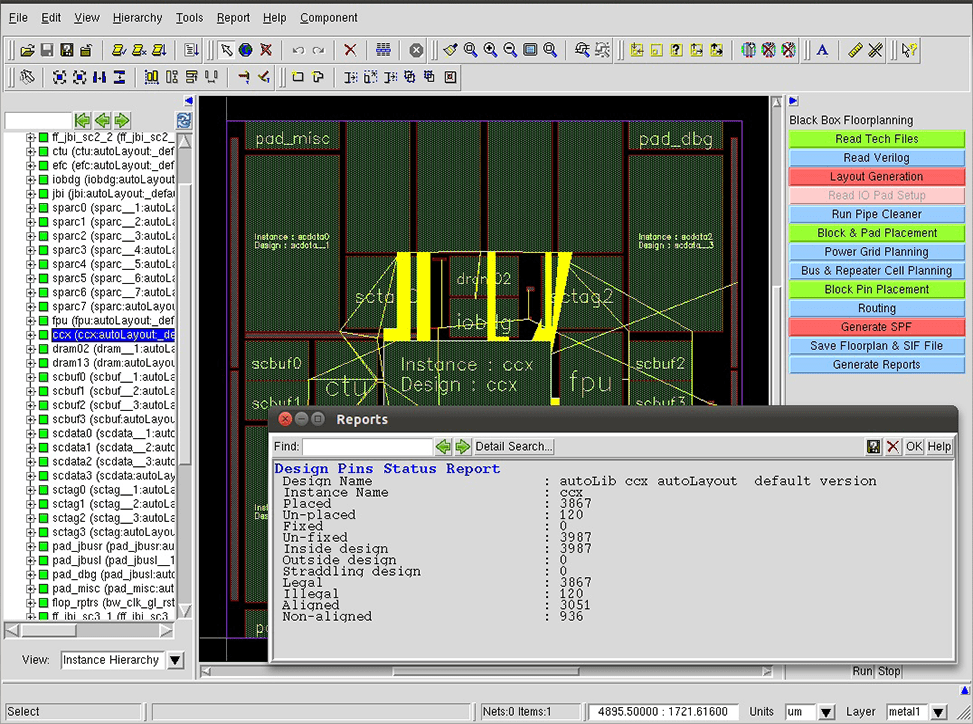

Unity Chip Planner

Fully hierarchical, top-down, and bottom-up floorplanning

Benefits

- Achieve design closure faster with the first and only top-down hierarchical floorplanner for custom design.

- Explore options and implement floorplans rapidly with accurate area and parasitic data.

- Obtain accurate parasitics for early simulation and static timing analysis.

- Execute ECOs quickly and precisely.

Key Features

- Hierarchical and pseudo-hierarchical floorplanning for custom design.

- Hierarchical area estimation, including custom digital and analog estimation.

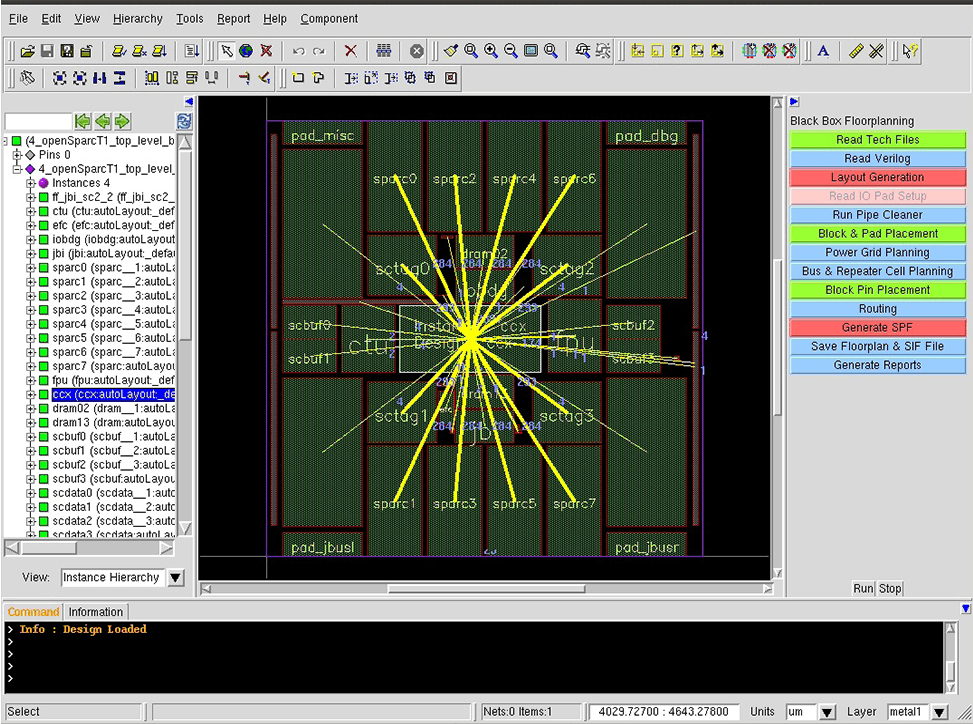

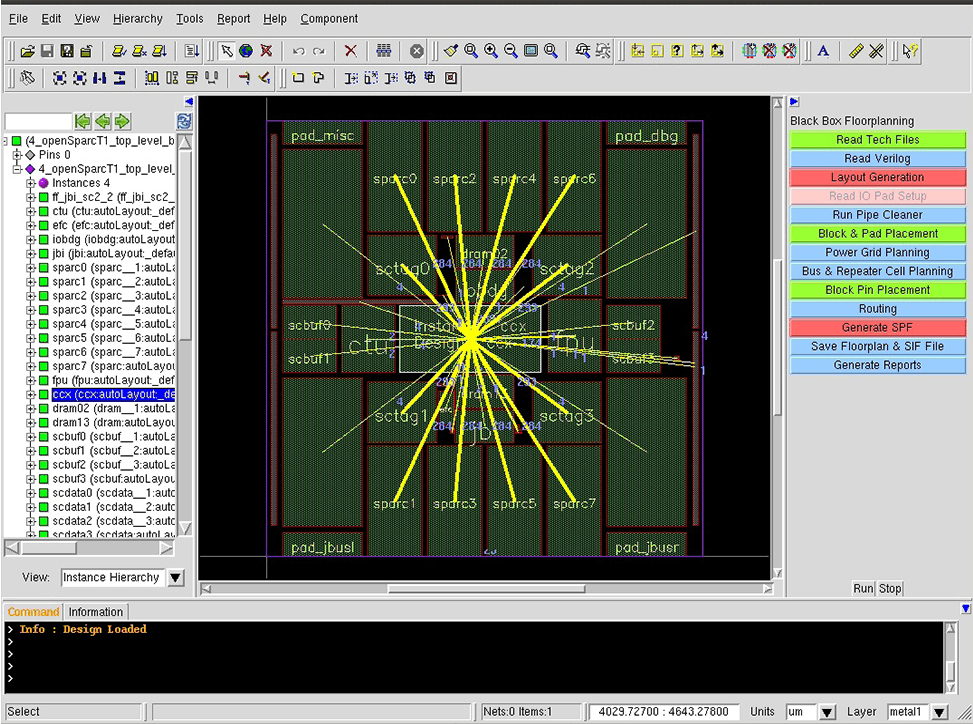

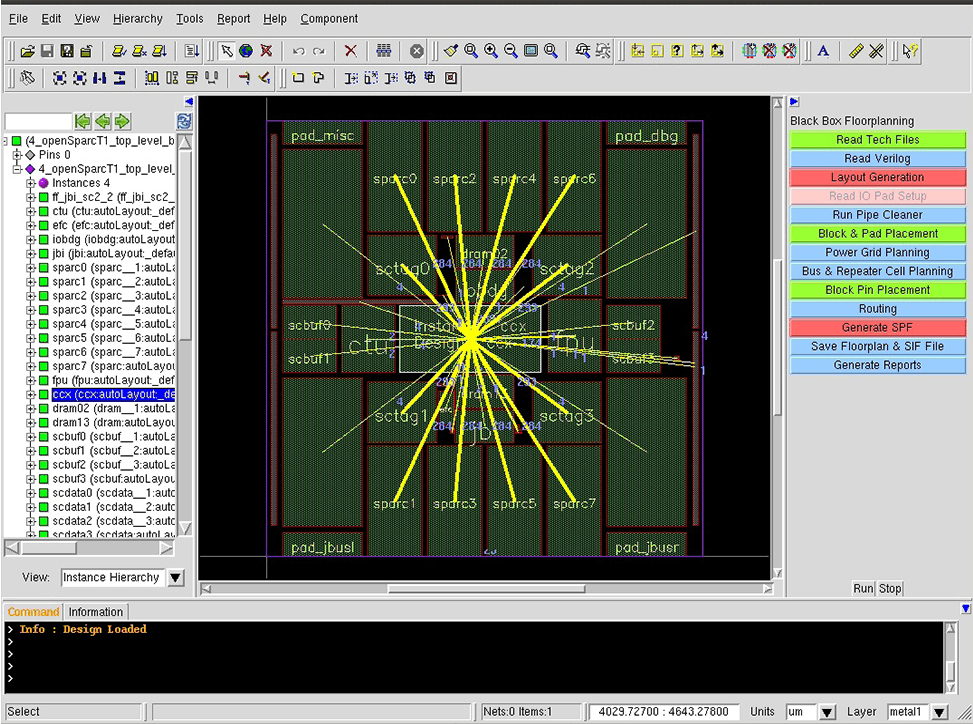

- Automatic block placement and softblock shaping.

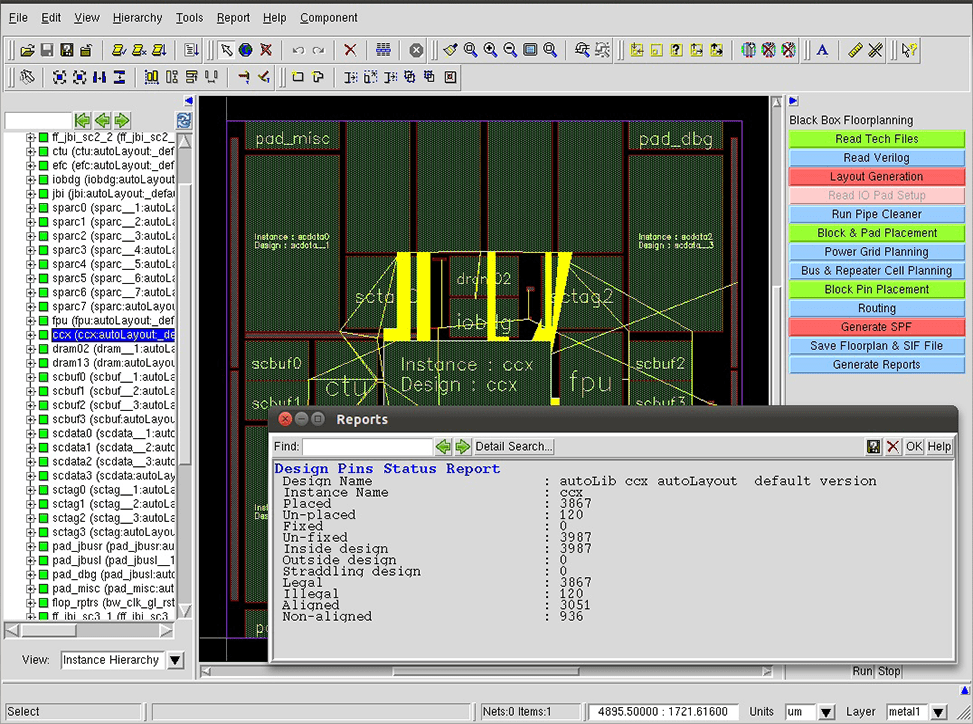

- Hierarchical automatic pin placement and sorting optimization.

- Intelligent, router-aware pin placement for efficient top-level routing.

- Fully integrated hybrid extraction engine for ‘real’ and estimated parasitics.

Made for Custom Digital

Custom designers face unique challenges such as large hard-IP blocks, analog content, few metal layers available for routing. At leading-edge nodes, process rules constrain designs in new ways, and the extreme aspect ratios of the routed wires and highly resistive metals make understanding parasitics critical. At Pulsic, we’ve worked closely with leading-edge custom designers for over 10 years. The vital insight gained has been utilized in the development of Unity Chip Planner to address the unique needs of custom design.

A new approach

Automated, hierarchical floorplanners are a standard part of the digital design flow. However, they don’t address the unique needs of custom design. So, until now, many custom design teams have struggled with bottom-up, manual assembly methodologies that lack a global understanding of a chip’s routing congestion and top-level parasitic data for simulation until the chip is almost complete. With these manual approaches, lack of automation and hierarchy management waste design effort and silicon resource. The frequent netlist changes that are a natural part of a leading-edge design process are difficult to manage manually and can cause major delays.

Faster Design Closure

By providing a high level of automation, Unity Chip Planner gives accurate results quickly and enables custom design teams to respond to netlist changes quickly and easily. Unity Chip Planner provides all the necessary tools and technologies within a fully integrated floorplanning environment. The guided flow offered in Unity Chip Planner helps ensure faster design closure with successful results, every time.

Rapid Floorplan Prototyping

Efficient, effective custom design floorplanning requires a series of top-down optimizations, followed by a bottom-up optimization, that determines pin placement in consideration of the block placement at lower levels of hierarchy, then uses those pin placements as the backbone of communication between levels of hierarchy.

Tight design cycles rarely afford custom designers the time to explore different floorplans to find the best fit for the die area. The Unity Chip Planner has a flexible and easy-to-configure interface that enables designers to explore different packages and prototype multiple floorplan topologies quickly to find the optimal use of the die area allocated for the design.

Unity Chip Planner Datasheet

Enter your details below to download the datasheet. Immediate download.